# Analysis and Simulation of the Impact of Gamma parameter and Phase Noise on Phase-Locked Loop with PID Controller

# G. Konwar and T. Bezboruah

Gauhati University, Department of Electronics & Communication Technology, Guwahati-781014, Assam, India Email: geetak222@gmail.com; zbt\_gu@yahoo.co.in

Abstract-In this work, detailed simulation and analysis of impact of gamma parameter and phase noise on the proportional-integral-derivative controlled phase-locked loop is carried out. The linear mathematical model for gamma parameter along with the phase noise model of the proposed system is developed. To improve the loop dynamics, a new type of loop filter is designed by considering a parallel combination of second order passive low pass filter and a proportional-integral-derivative controller in place of the traditional loop filter. The transfer function of gamma parameter as well as noise sources of each component of the phase-locked loop is derived from the proposed model in s-domain. Simulation is carried out on MATLAB to study how gamma parameter impacts on system response as well as on the phase noise contribution to the proposed system. The impact of gamma parameter on lock time, phase margin and loop bandwidth is also studied for gamma parameter less than one and greater than one. Finally, a comparison is done between second order low pass filter, proportional-integral-derivative controller and the newly designed loop filter. Simulation results shows that the proposed system with newly designed loop filter improves the system stability with fast switching speed and reduced the phase noise with gamma greater than one.

*Index Terms*—Gamma parameter, passive low pass filter, stability, phase noise, PID controller, Settling time

## I. INTRODUCTION

Phase-locked loops (PLL) are one of the most crucial circuits in modern electronic system which has significantly toward contributed the technology advancement in wireless communication since 1930s [1]. PLL is a control system which maintains the same phase between the input and the output signal. In communication systems [2]-[6], they are used in synchronization and demodulation circuits. Moreover, for jitters [3], [4], [7] and noise reduction, the PLL is commonly used. Use of PLL in the frequency synthesizers (FS) is one of its most common applications [4], [5]. In microprocessors [3], [5], [7], they are used in the generation of stable system clock. PLL consists of a phase detector (PD), loop filter (LF), voltage controlled oscillator (VCO) and a frequency divider (FD) [1], [5], [6], [8]-[10]. In the VCO, as the control voltage changes, the frequency of the oscillation also changes. Whenever the loop is turned on, the VCO runs at the centre frequency or free-running frequency. The PD compares the reference signal with the oscillator frequency and based on that error signal is generated. This error signal is passed through a low pass filter (LPF) which further generates the error voltage. Based on this error voltage, the VCO either increases or decreases the oscillation until the oscillator locks to the input frequency [6], [7], [9]. Under the locked condition, there may be no phase difference or a constant phase difference between the two signals. A PLL can acquire the lock only if the input signal is within the capture range of the PLL.

In PLL, the most challenging task is to design a stable LF which does not produce unwanted high frequency spurious oscillations [8], [11], [12]. The LF determines the PLL loop bandwidth (BW) which impacts the phase noise (PN), spurs and switching speed [1], [5], [8], [13]. The closed loop transfer function (TF) of a PLL has a huge impact on PN, spurs and lock time (LT) [8], [10], [11]. The PLL loop BW is the most critical parameter that impacts these performance metrics. Outside the loop, PN includes primarily the VCO. Inside the loop, PN includes pretty much everything aside from loop BW. Other parameters are phase margin (PM) [1], [11], [14], [15], gamma  $(\gamma)$  [9], [11], [16] and pole-ratios [15]. If either of the divider value of the FD or PD gain or VCO gain is changed significantly, then this will change the loop dynamics which necessitates redesigning of the LF.

Considering the above problems the LF is redesigned as a parallel combination of a 2<sup>nd</sup> order passive LPF (PLPF) and a proportional-integral-derivative controller (PIDC) in the proposed work. We study the impact of  $\gamma$ on the system response as well as on LT, PM and loop BW.  $\gamma$  is directly proportional to the PM and LT of the PLL. Again, LT is inversely related to the loop BW [11]. It is dependent on the PM in such a way that slight increase in  $\gamma$  value greater than one may lead to a maximum PM for frequency smaller than loop BW. On the other hand,  $\gamma < 1$  may lead to maximum PM at a frequency greater than the loop BW [9]-[11]. Thus, by

Manuscript received May 25, 2021; revised August 10, 2021; accepted September 9, 2021.

Corresponding author: G. Konwar (email: geetak222@gmail.com).

choosing the optimal value of  $\gamma$ , one can maximize the LT with optimal value of PM. Generally, in most of the applications,  $\gamma < 1$  is used for circuit implementations but this leads to sluggish LT as well as large PN. At  $\gamma = 1$ , one can achieve maximum achievable PM but with small loop BW. Consequently, simulation for  $\gamma > 1$  is carried out by considering different test cases to show how higher value of  $\gamma$  can provide fast LT with suitable PM and maximum loop BW. We also study the noise contribution of each source of the system to the output spectrum. A comparison of the designed LF is done with  $2^{nd}$  order PLPF and PIDC to verify the improvements of the proposed system.

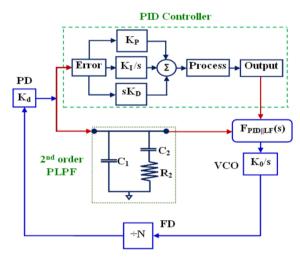

Fig. 1. Proposed model with TF of each component.

#### II. PROPOSED MATHEMATICAL MODEL

Fig. 1 shows the block diagram of the proposed system with TF of PD, VCO and FD including the proposed LF. The proposed PID||LF filter keeps the phase difference of the PD to zero by acting on the VCO. The PID||LF output is filtered and converted to the frequency, divided down by the FD, which is applied to the reference oscillator.

# A. Derivation of System TF

The TF of the proposed system can be mathematically expressed as:

$$H(s) = \frac{K_d F_{\text{PID}||\text{LF}}(s) \frac{K_0}{s}}{1 + \frac{K_d K_0 F_{\text{PID}||\text{LF}}(s)}{sN}}$$

(1)

where,  $K_d$  is the gain of the PD (in V/rad).  $K_0/s$  is the VCO TF with gain coefficient  $K_0$  (in rad/s/v). Integration of the control voltage is performed within the VCO which results in a factor of 1/s appearing in the TF of the loop. The TF of the FD is 1/N. The filter TF ( $F_{\text{PID}//\text{LF}}(s)$ ) is derived by integrating individual TF of the PIDC and the 2<sup>nd</sup> order PLPF as:

$$F_{\text{PID}||\text{LF}}(s) = F_{\text{2nd}}(s) \parallel F_{\text{PID}}(s) \tag{2}$$

A PIDC that comprises of individual proportional (P), integral (I) and derivative (D) controller is widely used in

feedback control of industrial processes due to its properties of reducing error, fast response, low complexity and cost [1], [14], [17]-[18]. Due to its fast settling and low noise property [19], it can be used as an efficient filter in the PLL system. The TF of the PIDC in terms of the proportional gain constant ( $K_P$ ), integral gain constant ( $K_D$ ) and time constants are given by:

$$F_{\text{PID}}(s) = K_{P} + \frac{K_{I}}{s} + sK_{D} = K_{P} \left( 1 + \frac{1}{T_{I}s} + sT_{D} \right) \quad (3)$$

$$T_I = K_P / K_I$$

=Integral time constant (4)

$$T_D = K_D / K_P$$

=Derivative time constant (5)

The  $2^{nd}$  order LF is the least complex LF that provides less resistor thermal noise and improves the spur levels [1], [11]. The  $2^{nd}$  order loop in particular is useful because it provides zero phase error when the incoming signal is of a fixed frequency or changes its phase at a constant rate. The TF of the  $2^{nd}$  order PLPF can be derived as:

$$F_{2nd}(s) = \frac{1 + s\tau_2}{sA_0(1 + s\tau_1)} = \frac{1 + sR_2C_2}{s^2R_2C_1C_2 + s(C_1 + C_2)}$$

(6)

where,  $\tau_1$  and  $\tau_2$  are the time constants and  $A_0$  is the LF capacitance and can be represented as:

$$T_1 = \frac{R_2 C_1 C_2}{A_0}$$

(7)

$$C_2 = R_2 C_1 \tag{8}$$

$$A_0 = C_1 + C_2 \tag{9}$$

The required TF of the newly designed LF of the proposed system can be derived by substituting (3) and (6) into (2) and assuming  $P_1=C_2R_2$ ,  $P_2=C_1+C_2$  and  $P=C_1P_1$  as:

$$F_{\text{PID} \parallel \text{LF}}(s)$$

$$\frac{s^{3}P_{1}K_{D} + s^{2}(K_{D} + P_{1}K_{P}) + s(K_{P} + P_{1}K_{I}) + K_{I}}{s^{4}PK_{D} + s^{3}(P_{2}K_{D} + PK_{P}) + s^{2}(P_{2}K_{P} + PK_{I} + P_{1}) + s(1 + P_{2}K_{I})}$$

(10)

For further simplification of equation (10), we assume that  $K_D+P_1K_P=Z_1$ ,  $K_P+P_1K_I=Z_2$ ,  $P_2K_D+PK_P=Z_3$ ,  $I+P_2K_I=Z_4$ ,  $P_2K_P+PK_I+P_1=Z$ ,  $P_1K_D=a$ , and  $PK_D=b$ . Therefore (10) can be rewritten as:

$$F_{\text{PID}||\text{LF}}(s) = \frac{s^3 a + s^2 Z_1 + s Z_2 + K_I}{s^4 b + s^3 Z_3 + s^2 Z + s Z_4}$$

(11)

Equation (11) improves the loop dynamics with fast switching speed and provides low PN as well as high system stability for various values of  $\gamma$ .

The overall TF of the system is therefore derived by substituting (11) into (1) and assuming the loop gain (LG) constant,  $K = K_d K_0 / N$  as:

$$H(s) = \frac{KN[s^{3}a + s^{2}Z_{1} + sZ_{2} + K_{I}]}{s^{5}b + s^{4}Z_{3} + s^{3}(Z + Ka) + s^{2}(Z_{4} + KZ_{1}) + sKZ_{2} + K_{I}K}$$

(12)

# B. Derivation of TF of Gamma

The  $\gamma$  optimization factor is one of the most important parameter in loop filter design of a PLL. It is a variable whose value is always greater than zero. Optimal choice of  $\gamma$  is helpful to reduce in-band noise and the peaking due to the VCO. Besides, it is useful to obtain a maximum achievable loop BW by making the value of  $\gamma$ greater than one. But large  $\gamma$  can degrade the system LT. The  $\gamma$  defines the system stability in terms of PM. The value of  $\gamma$  is dependent on the loop BW and used filter's time constants [9], [11], [16]. For 2<sup>nd</sup> order PLPF, the TF of the  $\gamma$  can be derived as:

$$\gamma_{\text{PLPF}} = (2\pi BW_1)^2 \tau_2 \tau_1 \tag{13}$$

where,  $BW_1$  is the loop BW with  $2^{nd}$  order PLPF.

The TF of  $\gamma$  of the system with only PIDC is defined as:

$$\gamma_{\rm PID} = (2\pi B W_2)^2 T_D T_I \tag{14}$$

where, BW<sub>2</sub> is the loop BW with PIDC.

The  $\gamma$  for the system can be derived in terms of time constants of both 2<sup>nd</sup> order PLPF and the PIDC as:

$$\gamma_{\text{PID}||\text{LF}} = (2\pi BW_{\text{PID}||\text{LF}})^2 \tau_2 (\tau_1 + T_D + T_I)$$

(15)

where,  $BW_{PID||LF}$  is the loop BW of the proposed system.

The required TF of  $\gamma$  is therefore derived by substituting (4), (5), (7), (8) and (9) into (15) as:

$$\gamma_{\text{PID}||\text{LF}} = (2\pi BW_{\text{PID}||\text{LF}})^2 \times \frac{K_I K_P P_1^2 C_1 + (K_P^2 + K_D P_I) P_1 P_2}{K_I K_P P}$$

(16)

Equation (16) shows that  $\gamma$  depends on the mutual tuning of the PIDC gain parameters and the resistance and capacitances used to design the 2<sup>nd</sup> order PLPF.

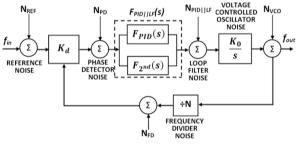

# C. Derivation of Noise TF

Fig. 2 shows the block diagram of the PN model of the proposed system to derive the noise TF of the system components. Each component in PLL building blocks generates noise to contribute to the total output noise spectrum. Although the noise model of reference oscillator and VCO can be similar but their contributions on the output noise are discrete owing to their placement in the feedback loop of the PLL. The PD detects the phase difference between the VCO and the reference oscillator, thus any random variation in the input of reference produces undesired VCO output and noise which affects the output spectrum. The LF produces noise according to the type and order of the filter used in the system. The noise produced by the FD directly appears at the input of PD after division by a factor of N [10], [20], [21]. Thus, each component of the system produces PN which affects the PLL stability [8, 15] and loop dynamics by creating phase variations of the PLL output signal. PN affects both the transmitted and received signal and distorts the modulation of transmitted data [2], [10]. The various noise sources of the PLL including the reference noise, PD noise, LF noise and FD noise are represented by  $N_{\text{REF}}$ ,  $N_{\text{PD}}$ ,  $N_{\text{PID}||\text{LF}}$ ,  $N_{\text{VCO}}$  and  $N_{\text{FD}}$  respectively. For accurate prediction of PN contribution of each source, the noise TFs is derived by considering Fig. 2.

The reference noise TF of the system can be derived as:

$$N_{\text{REF}}(s) = \frac{\text{Forward gain}}{1 + \text{Loop gain}}$$

(17)

where,

Forward gain =

$$K_d F_{\text{PID}||\text{LF}}(s) \frac{K_0}{s}$$

(18)

Loop gain =

$$K_d F_{\text{PID}||\text{LF}}(s) \frac{K_0}{s} \frac{1}{N}$$

(19)

Substituting (11), (18) and (19) into (17), the reference noise TF can be derived as:

$$N_{\text{REF}}(s) =$$

$$\frac{KN(s^{3}a + s^{2}Z_{1} + sZ_{2} + K_{I})}{s^{5}b + s^{4}Z_{3} + s^{3}(Z + Ka) + s^{2}(Z_{4} + KZ_{1}) + sKZ_{2} + K_{I}K}$$

(20)

The PD noise TF can be derived as:

$$N_{\rm PD}(s) = \frac{F_{\rm PID|LF}(s) \cdot (K_0/s)}{1 + \text{Loop gain}}$$

(21)

Fig. 2. Proposed PN model.

Substituting (11) and (19) into (21), the required noise TF of PD can be derived as:

$$N_{\rm PD}(s) = \frac{K_0(s^3a + s^2Z_1 + sZ_2 + K_I)}{s^5b + s^4Z_3 + s^3(Z + Ka) + s^2(Z_4 + KZ_1) + sKZ_2 + K_IK}$$

(22)

Contribution of filter noise to the output spectrum of the system is important as it removes the high frequency noise component of the PN of the reference signal. The LF noise TF of the proposed system is defined as:

$$N_{\text{PID}||\text{LF}}(s) = \frac{K_0/s}{1 + \text{Loop gain}}$$

(23)

Substituting (19) into (23) and assuming that  $P_1K_P=c$ , we can derive the required noise TF of the proposed LF as:

$$N_{\text{PID}||\text{LF}}(s) = \frac{K_0 \left[ s^5 b + s^4 Z_3 + s^3 (Z + Ka) + s^2 Z_4 \right] \right]}{s^6 b + s^5 Z_3 + s^4 Z + s^3 (Z_4 + Kc) + s^2 K Z_1 + s K Z_2 + K_1 K}$$

(24)

The VCO noise TF of the system is defined as:

$$N_{\rm VCO}(s) = \frac{1}{1 + \text{Loop gain}} \tag{25}$$

Substituting equations (11) and (19) into equation (25), the noise TF of VCO can be derived as:

$$N_{\rm VCO}(s) = \frac{N\left[s^5b + s^4Z_3 + s^3Z + s^2Z_4\right]}{s^5b + s^4Z_3 + s^3(Z + Ka) + s^2(Z_4 + KZ_1) + sKZ_2 + K_1K}$$

(26)

The FD noise TF of the system is defined as:

$$N_{\rm FD}(s) = \frac{2\pi N_{\rm REF}(s)}{K_d}$$

(27)

Substituting (20) into (27), the noise TF of FD can be derived as:

$$N_{\rm FD}(s) = \frac{2\pi}{K_d} \times \frac{KN(s^3a + s^2Z_1 + sZ_2 + K_I)}{s^5b + s^4Z_3 + s^3(Z + Ka) + s^2(Z_4 + KZ_1) + sKZ_2 + K_IK}$$

(28)

Equations (20), (22), (24), (26) and (28) are used for simulation of PN contribution of reference noise, PD noise, PID||LF noise, VCO noise and FD noise.

TABLE I: NUMERICAL VALUE OF DESIGN PARAMETERS FOR GAMMA AND PN

| Parameter | Value                    |                      |  |

|-----------|--------------------------|----------------------|--|

| Parameter | For y                    | For PN               |  |

| $K_d$     | 0.7-1.8V/rad             | 30V/rad              |  |

| $K_0$     | 20-35.714MHz/V           | 27MHz/V              |  |

| Ν         | 1.5                      | 6                    |  |

| $K_P$     | 50-105                   | $2.5e^{3}$           |  |

| $K_I$     | (500-1050)e <sup>9</sup> | $40e^{12}$           |  |

| $K_D$     | $(0.5-6)e^{-9}$          | 0.05e <sup>-12</sup> |  |

| $C_1$     | $(20-75)e^{-12}$         | $0.0001e^{-12}$      |  |

| $C_2$     | $(0.5-6)e^{-12}$         | 4.7e <sup>-12</sup>  |  |

| $R_2$     | (3.786-1.7123)Ω          | 20KΩ                 |  |

| DF        | -                        | 0.624                |  |

| PM        | -                        | $44^{0}$             |  |

\*"e" is used as standard scientific notation to represents the values of very large or very small

#### **III. SIMULATION AND RESULTS**

The values of various design parameters for  $\gamma$  and PN are given in Table I. The design parameters are chosen in such a way that the proposed system always remains stable. For  $\gamma$ , the values of each parameter are chosen in a specific range to achieve the required performance. Throughout the simulation, the values of capacitance  $C_1$ ,  $C_2$ , resistance  $R_2$  and the gain parameters  $K_D$ ,  $K_P$  and  $K_I$ are being varied within a specified range. Beyond this range as given in Table I, the system offers large peak as  $\gamma$ is directly related to the time constants of the filter. The PD and VCO gains  $K_d$  and  $K_0$  are also varied while the division ratio, N is kept constant. Throughout the simulation,  $K_d$  is varied in a range of 0.7V/rad to 1.8V/rad to have smallest margin of phase error. The VCO gain factor,  $K_0$  mainly affects the system PN and  $\gamma$  parameter. It is difficult to acquire a flat output power by increasing the frequency range of VCO as it increases the peaking.

To have minimal peaking with fast LT,  $K_0$  is varied in a range of 20-35.714MHz/V. Increasing N results in large LG. Therefore, to maintain the trade-off between large loop BW and fast LT, N is kept constant at 1.5 throughout the simulation. From the simulations of our proposed system, we have found that the range chosen for  $\gamma$  are best suited for high switching speed. Beyond this range, the system may give better stability but at the cost of degrading LT and PM above 95 deg.

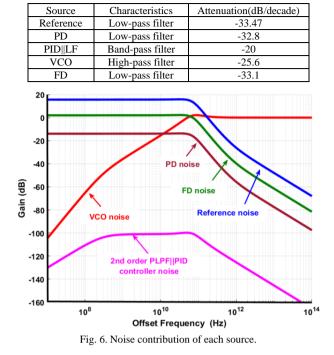

Similarly, the design parameters as shown in Table I for PN are chosen to attenuate the noise as low as possible within the stability limit. Usually, the reference noise, PD noise and FD is low-pass (LP) filtered while VCO noise is high-pass (HP) filtered and the LF noise is band-pass filtered. The design parameters of Table I are chosen to fulfill the above criteria. Beyond this range, the PIDC gain parameters  $K_P$ ,  $K_I$  and  $K_D$  results in high-pass (HP) characteristics for reference noise, PD noise as well as FD noise respectively while VCO shows low-pass (LP) characteristics. For values lower than considered, the proposed system shows large peaking on the response characteristics due to very small DF with infinite PM that leads to show HP characteristics for reference noise, PD noise and FD noise while LP characteristics for VCO noise.

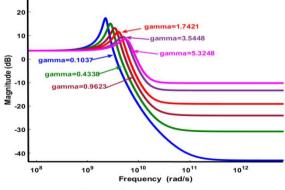

## A. Simulation for y

Equation (16) is considered for MATLAB simulation of  $\gamma$  to study the impact of  $\gamma$  on the system performance. Six different values of  $\gamma$  greater than and less than one are chosen to show the impact on system LT, PM and loop BW. The simulations results are shown in Table II while Fig. 3 shows the impact of  $\gamma$  on the proposed system. For  $\gamma < 1$ , it is seen from Fig. 3 that large peaking occurs. But, as the  $\gamma$  value is gradually increased above one, it increases the flatness of the response that means it removes the peaks. This implies, as we increase  $\gamma$  from 0.1037 to 5.3248, the percentage of overshoot (OS) decreases due to which the output response becomes more flattened. In general,  $\gamma$  is considered as one because large value of y degrades system LT [9], [11], [16]. However, from Table II, it is seen that increasing  $\gamma$ slightly greater than one not only decreases the peaking but also improves the LT of the system in the range of nanosecond (ns) as well as the VCO noise peak due to the addition of the PIDC with 2<sup>nd</sup> order PLPF. Also, higher value of  $\gamma$  leads to higher loop BW. Higher loop BW is responsible for low PN.

Fig. 3. Impact of  $\gamma$  on the proposed system.

| S. No | γ      | PM (deg) | LT (nS) | BW (GHz) |

|-------|--------|----------|---------|----------|

| 1     | 0.1037 | 30.3994  | 1.1358  | 0.56     |

| 2     | 0.4338 | 40.0302  | 0.90622 | 0.7      |

| 3     | 0.9623 | 50.3381  | 0.74626 | 0.85     |

| 4     | 1.7421 | 61.5902  | 0.63111 | 1.01     |

| 5     | 3.5448 | 80.4838  | 0.51    | 1.25     |

| 6     | 5.3248 | 94.3438  | 0.45068 | 1.41     |

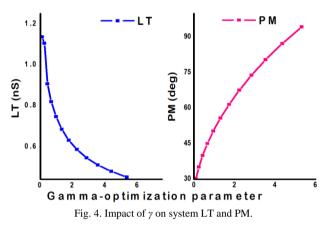

TABLE II: SIMULATION RESULTS FOR GAMMA

Fig. 4 shows the impact of  $\gamma$  on system LT and PM.  $\gamma$  is inversely proportional to the LT of the system while it is proportional to the PM. The LT decreases as a slow logarithmic ratio of frequency jump to tolerance, as  $\gamma$  is increased from 0.1037 to 5.3248. The higher the  $\gamma$ , the faster the PLL will be considered to be locked. The fastest LT of the system is 0.45068ns at  $\gamma = 5.3248$  with stable PM of 94.3 deg. PMs are determined from bode phase plot for different values of  $\gamma$  as given in Table II. PM relates to the stability of the PLL [1], [11], [21]. From Fig. 4, it is seen that, the PMs are positive and gradually increases from 30.3 deg to 94.3 deg with increasing  $\gamma$  from 0.1037 to 5.3248.

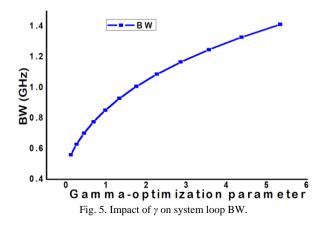

Fig. 5 shows the impact of  $\gamma$  on loop BW. The BW of the system is determined from MATLAB simulation by using the code "*bandwidth* (*sys*)", where "*sys*" is the TF of the system given by (12). The BW of the proposed system increases gradually from 0.56GHz to 1.41GHz with increasing  $\gamma$ . This improves the VCO noise and reference noise contribution to the output spectrum as the PLL output jitter decreases.

#### TABLE III: SIMULATION RESULTS FOR PN

## B. Simulation for PN

Table III shows the simulation results of each noise source of the system. The MATLAB simulation of noise characteristics is carried out referring (20), (22), (24), (26) and (28) in terms of Bode plot (magnitude) analysis. The results are shown in Fig. 6. The x-axis in Fig. 6 is the offset frequency in Hz and y-axis is the noise gain magnitude in dB. In the PLL circuit, the simulation of PN TF introduced by reference, PD and FD shows low pass filter (LPF) characteristics while the PN TF introduced by VCO shows high pass filter (HPF) characteristics [2], [7], [8], [10], [20]. In other words, the in-band PN of the frequency source loop is determined by the reference signal, the PD and the FD while the out-band PN of the frequency source loop is determined by the VCO. The PN TF introduced by the proposed LF shows band-pass filter (BPF) characteristics. The attenuation due to the PID||LF filter increases at +38dB/decade above the crossover frequency and decreases at -20dB/decade below the crossover frequency. The attenuation in the reference noise, the PD noise, the VCO noise and the FD noise decreases at the rate -33.47dB/decade, -32.8dB/decade, -25.6dB/decade and -33.1dB/decade respectively, below the crossover frequency.

## C. Impact of ST on y and PN

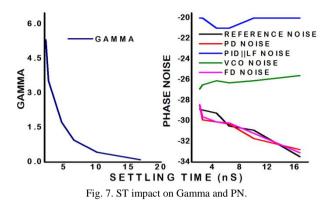

Fig. 7 shows the impact of settling time (ST) on  $\gamma$  and PN of the proposed system. It is observed that the ST decreases with increasing  $\gamma$ , i.e., larger value of  $\gamma$  provide fast switching speed. On the contrary, the reference noise, PD noise and FD noise inversely proportional to ST whereas the VCO noise and PID||LF noise is directly proportional to the ST. However, the variations are not linear. There are some fluctuations due to large OS which can be eliminated by considering larger value of  $\gamma$ .

# IV. COMPARATIVE ANALYSIS

The optimal choice of LF in the design of PLL is crucial to achieve accurate and sophisticated results within the stability limits. A comparison of the PID||LF with 2<sup>nd</sup> order PLPF and PIDC is analyzed to show the impact of LF on the PLL system dynamic characteristics.

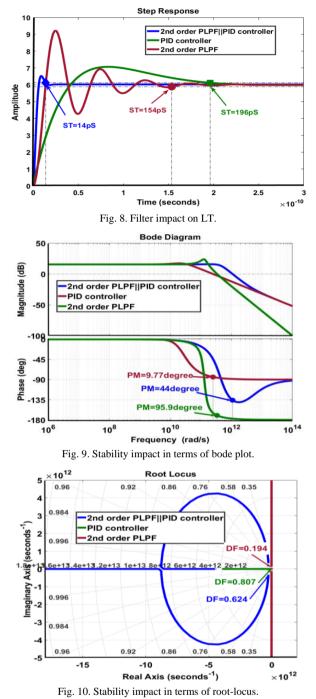

Fig. 8 shows the step response for PIDC, 2<sup>nd</sup> order PLPF and the proposed PID||LF filter. These plots represent the phase response to a step input for various damping factor (DF). For the same value of PD gain, VCO gain and FD division ratio, it is observed that a DF of 0.624 of PID||LF filter produces a peak OS of 8.69% which is less than 10% while DF of 0.807 and 0.109 for PIDC and 2<sup>nd</sup> order PLPF produces peak OS of 17.7% and 54.4% respectively, which are quite high. The low peak OS of the PID||LF filter improves the switching speed of the proposed PLL. The fastest LT of the PID||LF filter is 0.014nS which is 90% faster than that of the 2<sup>nd</sup> order PLPF and the PIDC at the same gain of PD and VCO with constant N. That means the switching speed of the proposed PID||LF is very fast which is essential for frequency hopping applications.

The stability of a PLL is one of the most important factors in practical applications. For a system to remain stable, the open LG magnitude should not be equal to unity and the phase angle should be less than 180 deg [11]. If the phase angle of  $[K_d K_0 F_{\text{PID}||LF}(s)/(sN)]$  is 180 deg, then equation (1) gives an infinite value resulting in an unstable system. When the phase angle is taken as zero deg, then the resultant system has minimal peaking with high stability. The relative stability of our proposed system is analyzed from the Bode-plot and Root-locus response as shown in Fig. 9 and Fig. 10 respectively along with the 2<sup>nd</sup> order PLPF as well as the PIDC. In practical applications, it has been observed that filters with PM less than 20 deg are likely to be more unstable and that with PM above 80 deg results in components either too large or negative [1], [11], [16]. In our simulations, it is observed from Fig. 8 and Fig. 9 that the PMs are positive and the roots of the respective characteristic equations for all the three filters are on the left-hand side of s-plane. This implies that all the three filters are stable. However for practical purpose, the proposed filter using 2<sup>nd</sup> order PLPF run in parallel with PIDC is found most suitable as it has PM of 44 deg and hence provides better stability than filters using individual 2<sup>nd</sup> order PLPF and PIDC.

Fig. 11 shows the effect of LFs for the same value of  $\gamma$ . is seen that, for  $\gamma = 0.1037$ , PIDC provides a flat

It is seen that, for  $\gamma = 0.1037$ , PIDC provides a flat response than that of the other two filters. For the proposed filter, a steeper peak is achieved due to the addition of the 2<sup>nd</sup> order PLPF. However, this peak can be reduced by considering  $\gamma > 1$  as shown in Fig. 3.

Fig. 12 shows the effect of LF on PN contribution. For  $2^{nd}$  order PLPF, the attenuation increases or decreases at the rate -20dB/decade both above and below the crossover frequency. For PIDC, the attenuation increases at the rate -21dB/decade above the crossover frequency and decreases at the rate -20dB/decade below the crossover frequency. For PID||LF, the attenuation increases or decreases at the rate -20dB/decade both above and below the crossover frequency. For PID||LF, the attenuation increases or decreases at the rate -20dB/decade both above and below the crossover frequency. It is observed

that the responses of PIDC and 2<sup>nd</sup> order PLPF exhibits steeper noise peaks whereas the PID||LF filter does not show any peak for the same value of DF and  $\gamma$ . A lot of literatures [2], [7], [8], [10], [11], [20] explained that noise peak always occurs due to LPF responses. However, from Fig. 12 it is clear that the noise peak due to filter can be removed by the addition of the newly designed PID||LF.

Table IV and Table V shows the comparison of the simulation results for  $\gamma$  and PN with earlier relevant works. From Table IV, it is seen that the proposed work provides fast LT of 0.45068ns at  $\gamma = 5.3248$  by using the parallel combination of the PIDC and the 2<sup>nd</sup> order PLPF than the other relevant works which uses different types of active and passive LF. From Table V, it is seen that due to the addition of PID||LF filter, the proposed system provides low noise attenuation than the other works that uses conventional  $2^{nd}$  or  $3^{rd}$  order active or passive LPF.

TABLE IV: COMPARISON OF RESULTS WITH EARLIER WORKS FOR GAMMA

| γ      | LT                     | Type of filter                                       |  |

|--------|------------------------|------------------------------------------------------|--|

| 5.3248 | 0.45068nS              | PID  LF                                              |  |

| 3.3    | <6 µS                  | 3 <sup>rd</sup> order type II PLF*                   |  |

| 6.0816 | 2.5nS                  | ALLF & SFA                                           |  |

| 1.024  | 249.9 µS               | 4 <sup>th</sup> order PLPF                           |  |

| 1.0709 | 91.176nS               | ALLF* & SFA*                                         |  |

|        | 3.3<br>6.0816<br>1.024 | 5.3248         0.45068nS           3.3         <6 μS |  |

\*PLF (passive loop filter) \*ALLF (active lead-lag filter)

\*SFA (standard approach feedback)

TABLE V: COMPARISON OF RESULTS WITH EARLIER WORKS FOR PN

| Work         | Attenuation (dB/decade) |       |         |       |       |                             |

|--------------|-------------------------|-------|---------|-------|-------|-----------------------------|

| WOIK         | Reference               | PD    | PID  LF | VCO   | FD    | Types of filter             |

| This<br>work | -33.47                  | -32.8 | -20     | -25.6 | -33.1 | PID  LF                     |

| [2]          | -30 to -40              | NA    | ≥-20    | ≈-40  | NA    | 2 <sup>nd</sup> order ALPF* |

| [7]          | -40                     | NA    | NA      | -40   | NA    | 2 <sup>nd</sup> order PLPF  |

| [10]         | -38                     | -38   | -20     | -40   | -38   | ALLF & SFA                  |

| [20]         | ≈-50                    | NA    | ≈-65    | ≈-28  | NA    | 3 <sup>rd</sup> order PLPF  |

#### V. CONCLUSION

The impact of  $\gamma$  on the system response, LT, PM and loop BW is studied along with the noise contribution of each source of the proposed PLL system by developing mathematical models for the newly designed PID||LF filter instead of traditional LPF. A comparison of the newly designed LF is done with conventional 2<sup>nd</sup> order PLPF and PIDC to show the improvements of loop dynamics of the system. It is observed that the proposed system not only improves the system stability and LT but also improves the loop dynamics. For  $\gamma > 1$ , the system shows lesser peaks with low PN, high switching speed and BW within positive PMs. The proposed system may be used for frequency hopping system and other industrial applications.

## CONFLICT OF INTEREST

The authors declare no conflict of interest.

## AUTHOR CONTRIBUTIONS

G. Konwar initiated the study, prepared the literature and wrote the manuscript before submission; T. Bezboruah revised the manuscript and prepared it for submission; all authors had approved the final version.

## ACKNOWLEDGMENT

The work is carried with the financial support of Visvesvaraya Ph.D. Scheme for Electronics & IT provided by Ministry of Electronics and Information Technology (MeitY), Govt. of India under grant number PhD-MLA/4(25)/2014.

## REFERENCES

- G. Konwar and T. Bezboruah, "Some aspects of modelling and [1] simulation of a high frequency and fast settling time proportionalintegral-derivative controlled phase-locked loop," presented at 2nd International Conference on Power, Energy and Environment: Towards Smart Technology, 2018.

- [2] A. Amornchai, A. Rangsiwatakapong, and D. Eungdamrong, "Simulation of mathematical phase noise model for a phaselocked-loop," presented at the 16th International Conference on Mathematical Theory of Networks and Systems, 2008.

- J. Kaur Sahani, A. Singh, and A. Agarwal, "A fast locking and [3] low jitter hybrid ADPLL architecture with bang bang PFD and PVT calibrated flash TDC," AEU-International Journal of Electronics and Communications, vol. 124, Sept. 2020.

- [4] H. Rahimpour, M. Gholami, G. Ardeshir, and H. MiarNaimi, "Low settling time all digital DLL for VHF application," International Journal of Engineering, Trans. C: Aspects, vol. 28, no. 3, pp. 419-425, March 2015.

- [5] D. Sulaiman, "Optimization of low power phase-locked loop design," Journal of Electrical and Electronics Engineering, vol. 13, no. 1, pp. 23-28, May 2020.

- [6] F. Al-Mutairi, R. Al-Mutairi, "Stability and nonlinear controller design of fast-lock phase-locked loop in 0.18-µm CMOS," Advances in Science, Technology and Engineering Systems Journal, vol. 2, no. 3, pp. 1266-1271, 2017.

- [7] A. Mehrotra, "Noise analysis of phase-locked loops," in *Proc. of IEEE/ACM International Conference on Computer Aided Design.*, 2000, pp. 277-282.

- [8] L. Jia, K. S. Yeo, J. G. Ma, M. A. Do, and X. P. Yu, "Noise transfer characteristics and design techniques of a frequency synthesizer," *Analog Integrated Circuits and Signal Processing*, vol. 52, pp. 89-97, Sept. 2007.

- [9] M. Borah and T. Bezboruah, "A study on *y*-optimization parameter and phase margin of fourth order phase-locked loop," *International Journal of Computer Sciences and Engineering*, vol. 6, no. 12, pp. 146-150, 2018.

- [10] K. Kalita and T. Bezboruah, "Modeling and behavioral simulation of noise transfer characteristics of a 2 GHz phased-locked loop for frequency synthesizer," *International Journal of Modern Engineering Research*, vol. 1, no. 2, pp. 615-625, 2011.

- [11] D. Banerjee, *PLL Performance, Simulation and Design*, Dogear publisher, 2017.

- [12] K. Rahbar and P. Crosby, "Phase locked loop with modified loop filter," U.S. Patent No. 9 503 254, November 22, 2016.

- [13] Y. Li and Z. Wu, "High-accuracy resolver-to-digital conversion via phase locked loop based on PID controller," *IOP Conference Series: Materials Science and Engineering*, vol. 339, #012003, 2018.

- [14] N. H. Nguyen and P. D. Nguyen, "Overshoot and settling time assignment with PID for first-order and second-order systems," *IET Control Theory & Applications*, vol. 12, no. 17, pp. 2407-2416, 2018.

- [15] M. K. M. Ali and O. Hashemipour, "Fast locking technique for phase locked loop based on phase error cancellation," *AEU-International Journal of Electronics and Communications*, vol. 109, pp. 99–106, Sept. 2019.

- [16] K. Kalita and T. Bezboruah, "Impact of γ-optimization parameters and phase margin on closed loop gain of phase-locked loop," *International Journal of Electronics and Communication Engineering*, vol. 6, no. 3, pp. 225-231, 2013.

- [17] S. Golestan, M. Mohammad, D. F. Francisco, and M. G. Josep, "Performance improvement of a prefiltered synchronousreference-frame PLL by using a PID-type loop filter," *IEEE Trans. on Industrial Electronics*, vol. 61, no. 7, pp. 3469-347, July 2014.

- [18] T. L. Mien, V. V. An, and B. T. Tam, "A fuzzy-PID controller combined with PSO algorithm for the resistance furnace," *Advances in Science, Technology and Engineering Systems Journal*, vol. 5, no. 3, pp. 568-575, 2020.

- [19] H. U. Uyanik and N. Tarim, "PID-controlled PLL for fast frequency-hopped systems," presented at the 6th IEEE Dallas Circuits and Systems Workshop on System-on-Chip, 2007.

- [20] S. A. Osmany, F. Herzel, K. Schmalz, and W. Winkler, "Phase noise and jitter modeling for fractional-N PLLs," *Advances in Radio Science*, vol. 5, pp. 313-320, July 2007.

- [21] K. C. Peng, W. L. Wu, and J. H. Lin, "Reduction of phase noise in fractional-N frequency synthesizer using self-injection locking loop," *IEEE Trans. on Microwave Theory and Techniques*, vol. 68, no. 9, pp. 3724-3731, 2020.

Copyright © 2021 by the authors. This is an open access article distributed under the Creative Commons Attribution License (CC BY-NC-ND 4.0), which permits use, distribution and reproduction in any medium, provided that the article is properly cited, the use is non-commercial and no modifications or adaptations are made.

Geetamoni Konwar received the B.Sc. degree in Electronics from Dibrugarh University, Assam in 2012 and the M.Sc. degree in Electronics & Communication Technology (ECT) from Gauhati University, Assam in 2014. She is currently a Ph.D. student in the department of ECT, Gauhati University, Guwahati, Assam, India. Her research interest includes wireless communication, telecommunication, control theory and signal processing.

**Tulshi Bezboruah** is currently working as Professor and Head of the Department of Electronics & Communication technology, Gauhati University, Assam, India. He received his M. Sc. & PhD deg in Physics (Specialization Electronics & Radio-Physics) from Gauhati University in 1993 and 1999 respectively. He joined Gauhati University as a Lecturer in the Department of Electronics & Communication Technology (Formerly Electronics Science), Gauhati University in

the year 2000. He became Associate Professor and Professor of the Department in the year 2007 and 2013 respectively. In the year 2014 he became the Head of the Department. He did his postdoctoral research on Embedded System for Instrumentation and Control at ICTP, Trieste, Italy during 2003- 2010 as Junior Associate of the Centre. Later on, he had been awarded Visiting Faculty Fellow by the Department of Science & Technology (DST), Govt. of INDIA at the Institute of Radio Physics & Electronics, Calcutta University in the year 2011.