# Inexpensive Fabrication of Sn-Ag-Cu/Cu:ZnO/Al/PET Memristive Devices through Unconventional Synthesis Techniques

Panati S. Sreenivas Reddy<sup>1,3</sup>, P. Michael Preetam Raj<sup>2</sup>, Sravan K. Vittapu<sup>3,\*</sup>, and K. Senthil Kumar<sup>1</sup>

<sup>1</sup> Department of Electronics and Communication Engineering, Dr MGR Educational and Research Institute,

Chennai, India

<sup>2</sup>Department of Computer Science and Engineering, MLR Institute of Technology, Hyderabad, India

<sup>3</sup> Department of Electronics and Communication Engineering, Nalla Narasimha Reddy Educational Society's Group of Institutions, Ghatkesar, India

Email: sreenivaspanati@gmail.com (P.S.S.R.), michaelraj38@gmail.com (P.M.P.R.), vsravan91@gmail.com (S.K.V.), ksenthilkumar@drmgrdu.ac.in (K.S.K.)

Abstract—In the last few decades there has been rapidly growing research interest in resistive switching devices which led to tremendous technological advancements. In this work, copper (Cu) doped zinc oxide (ZnO) thin film was deposited on Aluminum coated PET conductive sheets having a sheet resistance of 20  $\Omega$ . Soldering balls of 2 mm diameter consisting of 96.5% Sn, 3% Ag and 0.5% Cu alloy were dropped into this thin film to form the Sn-Ag-Cu/Cu:ZnO/Al/PET memristive devices. No additional annealing temperature was required as the heat transfer from 350 °C hot soldering ball onto the Cu:ZnO thin film was sufficient to anneal the thin film. The electronic characteristics of the device were obtained by employing a function generator and an oscilloscope instead of an expensive source meter. The elimination of redundant hot furnace (for annealing) and source meter (for I-V characterization) resulted in the improvement of total equipment expenses by ~96%.

*Index Terms*—Memristor, material science, resistive switching, non-volatile memory, nanoscale materials, oxide semiconductors

#### I. INTRODUCTION

At present, there is a great need for electronic devices which operate at low power with high switching rates in order to process huge volumes of data [1, 2]. In contrast, conventional silicon-based dynamic random-access memory (RAM), static RAM and flash memory have obnoxious issues such as inadequate switching speed, high power requirements and poor scalability which led to the renewed interest towards resistive switching (RS) devices [3]. Resistive switching devices are increasingly becoming vital entities in revolutionizing circuit design for the advancement of numerous electronic applications. RS is a physical phenomenon in which due to the exertion of the strong electric field or current there is a sudden change in the memristance of the active layer [4]. RS devices are Non-Von Neumann like architecture [5]. In typical computing systems, RS devices provide a high degree of parallelism [6–8]. Interestingly, besides non-volatile memory, RS device finds its uses in designing digital switches, flip-flops, logic gates, latches and memristive interconnections in field programmable gate array with low on-chip area, faster and low power consumption [9]. Moreover, RS have been utilized in analog electronic applications such as adaptive filters, tunable gain amplifiers and chaotic circuits [9]. Furthermore, recent developments in the field of artificial neural networks have shown the need for RS devices [10, 11].

The existence of missing fourth fundamental circuit element, which is a two-terminal passive device called memristor was first posited by Leon Chua in 1971 [12]. In 2008, it was eventually realized in HP labs [13]. Since last decade, the memristor has been an intrigued alternate conventional complementary metal-oxideto the semiconductor (CMOS) devices in electronic circuits [14]. By adapting the magnitude and polarity of external power supply, the memristor can further be tuned [15]. In various applications like neuromorphic computations, digital image processing, oscillator circuits, analog computers, signal recognition and digital logic systems, memristor finds its uses due to its inbuilt capability to store data in the form of memristance [14]. This memory capability of memristor has made revolutionary effects in the design of electronic circuits [14, 16].

From non-volatile memory to programming logic, the main attributes of memristor that makes it attractive for a number of applications are modest switching voltage (<3 V), high endurance (>  $10^6$  cycles), eminent on-chip area (~42%), faster switching rates (~5 ns), reduced power loss (~ $10^{-6}$  W), multi-bit (6 bits) operations and high information retention time (~10 years) when compared to the existing transistor technology [4, 17]. In this regard, recently, there have been an increase in the research interests to design novel RS based circuits and systems.

Manuscript received October 5, 2023; revised October 24, 2023; accepted November 4, 2023.

<sup>\*</sup>Corresponding author

The RS device conventional structure consists of an active layer squeezed in between two electrodes. The electronic resistance in RS device represents the data stored in it where a logic 0 indicates a low resistive state and logic 1 represents a high resistive state. RS property in oxide materials like Al<sub>2</sub>O<sub>3</sub>, ZrO<sub>2</sub>, SiO<sub>x</sub>, TiO<sub>2</sub> and Ta<sub>2</sub>O<sub>5</sub> was first observed by Hickmott in 1962 [18]. The first Au/SiO<sub>2</sub>/Al based RS cell structure was reported by Simmons and Verderber in 1967 [19]. After three decades, the research on RS thin films was accelerated by the group of Ignatiev [20]. Subsequently, a 64-bit Resistive RAM array was developed using the RS-CMOS hybrid technology which contains a 500 nm CMOS technology and Pr<sub>0.7</sub> Ca<sub>0.3</sub> MnO<sub>3</sub> RS device [21].

Recent developments in the field of RS device have led to a renewed interest in adoption of RS memories by multi-national companies like HP Labs, Samsung and Infineon [1, 9]. From the important features of RS device stated above, several electronic materials were exploited to obtain RS properties. To date, there has been a considerable amount of research carried out which tends to focus on RS devices in which, ferroelectric [19], ferromagnetic [20], perovskite oxides [21, 22], organic semiconductors [23], transition-metal oxides (TMOs) [3] and polymers [4] were used as active material. By considering several optimistic features like easy fabrication, low operating voltage, power reduction, improved scalability, compact integration and coexistence with widely used CMOS devices [24] and faster switching rates, ferroelectric materials and TMOs were most preferred.

A considerable amount of literature has been shown that the outstanding electrical and structural attributes were provided by TMOs including ZnO [25], HfO<sub>2</sub> [26], and TiO<sub>2</sub> [27-29]. After rigorous experimentation, researchers preferred ZnO as an active material [30, 31] due to its simple synthesis procedure, reduced processing temperature, built-in availability of oxygen deficiencies and ions. In order to amend the electrical conductivity, defects, oxygen vacancies, and ions, several attempts were made to promote the functionalities of the device by inserting the metal impurities into ZnO thin film [32]. To inscribe this, different metal dopants such as copper (Cu) [32], cobalt [33], titanium [29], vanadium [30], lithium [31], aluminium [32] and lanthanum [33] were studied. Among these impurities, copper (Cu) contains an electron shell which is analogous to Zinc (Zn) spawning it to conveniently accommodate into the ZnO thin film structure [25]. Central to the discipline of RS devices, an extremely important active layer for memristive applications is Cu:ZnO because in ZnO, Cu acts as an electron trap, increases resistivity, and makes ZnO to act as a ferroelectric material. Thus, in summary, it is shown that Cu:ZnO is extremely preferred as active layer for RS devices with suitable electrodes [3, 34-40].

## II. MATERIALS AND METHODS

The economical synthetic methods were employed for blending the Cu:ZnO thin film. To begin with, 657.2 mg of zinc acetate di-hydrate was supplemented with 0.3 mL of di-ethanolamine and 10 mL of isopropanol. The resultant solution was amalgamated for 10 min at room temperature. Subsequently, 29 mg copper (II) acetate monohydrate was added to the resultant zinc acetate ensued by blending for 120 min at 330 K. This final solution was aged for 24 h. In our previous work [4], the physical characteristics of Cu:ZnO thin film were presented in detail.

### III. RESULTS AND DISCUSSIONS

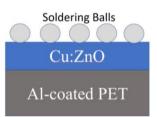

Over the past few decades, the Al/PET conductive sheets are manufactured in bulk, widely used in food packaging applications and are available for negligible costs [39]. In this work, the solution of Cu:ZnO was dipcoated onto the Al/PET conductive sheet having a sheet resistance of 20  $\Omega$ . Thereafter, the deposited thin film was dried for 24 h at room temperature. As a result, ~50 nm Cu:ZnO thin film was deposited on Al/PET conductive sheet. It is important to mention that 96.5% Sn. 3% Ag and 0.5% Cu allov is widely being used as soldering material. In order to reduce fabrication expenses through utilizing this already available material as electrode, soldering balls of 2 mm diameter consisting of this alloy were dropped onto the Cu:ZnO thin film to form the Sn-Ag-Cu/Cu:ZnO/Al/PET memristive devices shown in Fig. 1, where soldering ball was employed as top electrode and Al/PET conductive sheet acted as a bottom electrode with Cu:ZnO thin film as the active layer.

Fig. 1. Schematic of the fabricate d Sn-Ag-Cu/Cu:ZnO/Al/PET device architecture. Copper (Cu) doped zinc oxide (ZnO) thin film was deposited on aluminium coated PET conductive sheets having a sheet resistance of 20  $\Omega$ . Soldering balls of 2 mm diameter consisting of 96.5% Sn, 3% Ag and 0.5% Cu alloy were dropped into this thin film to form the Sn-Ag-Cu/Cu:ZnO/Al/PET memristive devices.

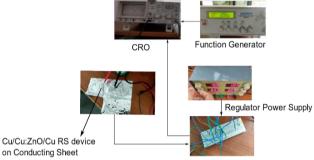

It is important to mention that the temperature of soldering balls was ~350 °C. When these balls were dropped into the deposited thin film, heat transfer took place from the soldering balls to the Cu:ZnO thin film. This transfer was sufficient to anneal the Cu:ZnO thin film; no additional hot furnace was essential to anneal the thin film. The electronic characteristics of the device were obtained by employing a SM5060-2 function generator and a Scientific 30 MHz SM410 oscilloscope instead of an expensive source meter. The fabricated Sn-Ag-Cu/Cu:ZnO/Al/PET RS device is connected to the current to voltage converter which is depicted in Fig. 2. The function generator was employed to generate a sine signal of 2 V amplitude and 25 Hz frequency. On the other side, the cathode ray oscilloscope (CRO) was employed to obtain the electronic device characteristic plots. In order to obtain these features, the current through the RS device was modified into a voltage signal through the employment of a current to voltage converter.

It is noteworthy to mention that ~10 V was supplied to each to the inverting and non-inverting terminals of the operational amplifier of the converter circuit. This converted signal was provided at the first channel (Y), nevertheless, the voltage across the memristive device was supplied to the second channel (X) of CRO which was engaged in its X-Y mode to obtain the room temperature *I-V* characteristics of the proposed RS device. The pinched hysteresis loop which indicates the signature of the memristor was obtained on the CRO as showcased in Fig. 2. Similar results were obtained through simulation roots.

Current to Voltage Converter

Fig. 2. Fabricated Sn-Ag-Cu/Cu:ZnO/Al/PET RS device connected to the current to voltage converter circuit. Function generator was employed to generate the sinusoidal signal whereas regulated power supply was engaged to supply the biasing voltage which is essential for the operational amplifier. The oscilloscope was functioned in its X-Y mode of operation.

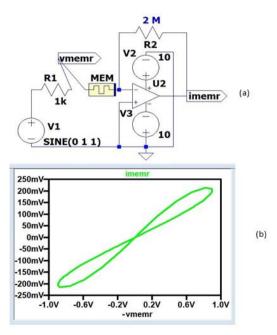

Fig. 3. (a) Circuit to convert current through memristor into the corresponding voltage signal, (b) and its plot on an oscilloscope. A 1 V and 1 Hz sinusoidal signal was applied as an input to memristor MEM through resistor R1. The operational amplifier U2, resistance R2, voltage sources V2 and V3 were utilized to convert the current through the memristor into the appropriate voltage signal. The plot between the memristive voltage - $v_{memr}$  and the output voltage at  $i_{memr}$  depicted a pinched hysteresis graph.

Fig. 3(a) presentations the spice simulation of circuit which was employed to convert current through memristor into the corresponding voltage signal. A 1 V and 1 Hz sinusoidal signal was supplied to this circuit. The resistor R1 was engaged to defend the memristor MEM while the operational amplifier U2, resistor R2, voltage sources V2 and V3 were hired to modify the memristive current into the proportional voltage signal. The memristive voltage was represented as  $v_{\text{memr}}$  while the memristive current (in the form of voltage) was presented as  $i_{\text{memr}}$ . The mathematical relationships of the *I-V* curve were given by the following equations:

$$i_{\rm memr} = 0.003 - 0.15v_{\rm memr} + 0.007v_{\rm memr}^2 \tag{1}$$

$$i_{\rm memr} = -0.004 - 0.43v_{\rm memr} + 0.21v_{\rm memr}^2 \tag{2}$$

$$i_{\rm memr} = 0.003 - 0.41v_{\rm memr} + 0.18v_{\rm memr}^2 \tag{3}$$

$$i_{\rm memr} = -0.005 - 0.12v_{\rm memr} + 0.11v_{\rm memr}^2 \tag{4}$$

It is noteworthy to mention that Eq. (1) was obtained for the rising part of the curve along the positive  $i_{memr}$  axis, whereas Eq. (2) corresponded to the falling part of the curve in the first quadrant. It is important to mention that  $i_{memr}$  is the output terminal and thus the output voltage is at  $i_{memr}$ . Kindly note that  $i_{memr}$  represents the memristive current which was converted into the voltage at output through current to voltage converter. Consequently, Eq. (3) and Eq. (4) represent the rising and falling parts of the  $i_{memr}$  curve in the third quadrant.

The general form of the above equations is given as

$$\mathbf{i}_{\text{memr}} = \mathbf{X} + \mathbf{Y} v_{\text{memr}} + \mathbf{Z} v_{\text{memr}}^2 \tag{5}$$

The abovementioned relations can be vectorized into a lookup table for the modelling and simulation purpose as shown in Table I.

TABLE I: 2-D VECTORIZED REPRESENTATION OF THE I-V CHARACTERISTICS

| Quadrant | Х      | Y     | Z     |

|----------|--------|-------|-------|

| Q1 rise  | 0.003  | -0.15 | 0.07  |

| Q1 fall  | -0.004 | -0.43 | -0.21 |

| Q3 rise  | 0.003  | -0.41 | 0.18  |

| Q3 fall  | -0.005 | -0.12 | -0.11 |

As disclosed in Fig. 3(b), the  $-v_{memr}$  versus  $i_{memr}$  plot was found to be a pinched hysteresis loop which represents the signature of the memristor, analogous to the *I-V* curve of the fabricated device depicted in the CRO of Fig. 2. This confirms that the Sn-Ag-Cu/Cu:ZnO/Al/PET memristor was successfully fabricated and characterized using inexpensive fabrication techniques through the elimination of redundant hot furnace (for annealing) and source meter (for I-V characterization). It is well known in literature that memristor exhibits randomness in its device characteristics [41]. However, electronic circuit design was efficiently performed such that the effects of randomness were mitigated in the overall performance of the memristive circuit [42, 43]. Furthermore, the memristance varies with temperature dependencies and other circuit elements connected to it, in addition to its stochastic behaviour [42, 43]. However, these drawbacks which are evident at the device level have been neutralised at the circuit level design [42, 43]. The proposed techniques are also valid even for other models of CRO & function generator as long as the signals generated and measured are within the specified range of these equipment. It is important to mention that these model variations do not adversely affect the memristive characteristics [43].

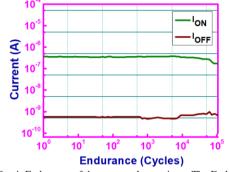

Based on the experimental data shown in Fig. 4, the memristor exhibited switching time dependent endurance property of  $>10^5$  cycles. Grounded on the prolonged switching characteristics, it was identified that the memristor exhibited data retention time of >10 years. Therefore, the proposed memristor exhibited favorable characteristics for data storage applications.

Fig. 4. Endurance of the proposed memristor. The Endurance was found to be stable for  $>10^5$  cycles.

When compared to the traditional synthesis methods [1, 4, 17, 22, 40], the techniques presented in this work resulted in ~96% improvement of total equipment expenses. Such improvements were primarily owing to the employment of unconventional device characterization techniques. Furthermore, it is interesting to note that the device was fabricated and validated without the employment of clean room facilities.

### IV. CONCLUSION

In summary, the proposed Cu:ZnO thin film was fabricated upon Al/PET conductive sheet. Soldering balls were employed as top electrode and the conductive sheet as the bottom electrode with Cu:ZnO thin film as the active layer in the proposed Sn-Ag-Cu/Cu:ZnO/Al/PET RS device. The utilization of the oscilloscope and function generator in order to obtain the *I-V* characteristics and the employment of heat from soldering rod instead of expensive hot furnace resulted in the improvement of total equipment expenses by ~96%. Importantly, the device was successfully fabricated and validated without the employment of clean room facilities. The ideas presented in this work pave the way for the futuristic inexpensive synthesis of memristive integrated circuits and systems.

#### CONFLICT OF INTEREST

The authors declare no conflict of interest.

## AUTHOR CONTRIBUTIONS

Panati S Sreenivas Reddy, Michael Preetam Raj and Sravan K. Vittapu conducted the research; Panati S Sreenivas Reddy, P Michael Preetam Raj and Sravan K. Vittapu analyzed the results during experimentation; Panati S Sreenivas Reddy wrote the paper; K. Senthil Kumar has given valuable inputs in every stage of the research all authors had approved the final version.

#### REFERENCES

- E. Carlos, R. Branquinho, R. Martins, A. Kiazadeh, and E. Fortunato, "Recent progress in solution-based metal oxide resistive switching devices," *Advanced Materials*, vol. 33, no. 7, #2004328, Feb. 2021.

- [2] S. Aminizadeh, A. Heidari, S. Toumaj *et al.*, "The applications of machine learning techniques in medical data processing based on distributed computing and the internet of things," *Computer Methods and Programs in Biomedicine*, Aug. 2023. doi: 10.1016/j.cmpb.2023.107745

- [3] D. Ielmini, "Resistive switching memories based on metal oxides: Mechanisms, reliability and scaling," *Semicond. Sci. Technol.*, vol. 31, no. 6, #063002, May 2016.

- [4] P. K. R. Boppidi, P. M. P. Raj, S. Challagulla *et al.*, "Unveiling the dual role of chemically synthesized copper doped zinc oxide for resistive switching applications," *Journal of Applied Physics*, vol. 124, no. 21, #214901, Dec. 2018.

[5] Z. Wang, H. Wang *et al.*, "Influence of Cu dopant on the

- [5] Z. Wang, H. Wang *et al.*, "Influence of Cu dopant on the electronic and optical properties of graphene-like ZnO monolayer," *Physica E: Low-Dimensional Systems and Nanostructures*, vol. 115, #113702, Jan 2020.

- [6] A. Kiazadeh, E. Fortunato *et al.*, "Design and synthesis of low temperature printed metal oxide memristors," *Journal of Materials Chemistry C*, vol. 9, no. 11, pp. 3911–3918, 2021.

- [7] M. K. Song, J. H. Kang, X. Zhang *et al.*, "Recent advances and future prospects for memristive materials, devices, and systems," *ACS Nano*, vol. 17, no. 13, pp. 11994–12039, June 2023.

- [8] T. Soliman, N. Laleni, T. Kirchner et al., "FELIX: A ferroelectric FET based low power mixed-signal in-memory architecture for DNN acceleration," ACM Trans. on Embedded Computing Systems, vol. 21, no. 6, pp. 1–25, Oct. 2022.

- [9] S. Kundu, P. B. Ganganaik, J. Louis, H. Chalamalasetty, and B. P. Rao, "Memristors enabled computing correlation parameter inmemory system: A potential alternative to von Neumann architecture," *IEEE Trans. on Very Large Scale Integration (VLSI) Systems*, vol. 30, no. 6, pp. 755–768, 2022

[10] H. Zhao, Z. Liu *et al.*, "Memristor-based signal processing for

- [10] H. Zhao, Z. Liu *et al.*, "Memristor-based signal processing for edge computing," *Tsinghua Science and Technology*, vol. 27, no. 3, pp. 455–471, Nov 2021.

- [11] Z. Cao, B. Sun, G. Zhou et al., "Memristor-based neural networks: A bridge from device to artificial intelligence," Nanoscale Horizons, 2023. doi: 10.1039/D2NH00536K

- [12] L. Chua, "Memristor-the missing circuit element," *IEEE Trans. on Circuit Theory*, vol. 18, no. 5, pp. 507–519, Sep. 1971.

- [13] D. B. Strukov, G. S. Snider, D. R. Stewart, and R. S. Williams, "The missing memristor found," *Nature*, vol. 453, no. 7191, pp. 80–83, May 2008. doi: 10.1038/nature06932

- [14] P. Marani, G. Gelao, and A. G. Perri, "A review on memristor applications," arXiv preprint, 2015. doi: 10.1145/3233987

- [15] O. Kavehei, A. Iqbal *et al.*, "The fourth element: characteristics, modelling and electromagnetic theory of the memristor," in *Proc. the Royal Society A: Mathematical, Physical and Engineering Sciences*, vol. 466, no. 2120, pp. 2175–2202, 2010.

- [16] A. Isah and M. J. Bilbault, "Review on the basic circuit elements and memristor interpretation: Analysis, technology and applications," *Journal of Low Power Electronics and Applications*, vol. 12, no. 3, Aug. 2022. doi: 10.3390/jlpea12030044

- [17] S. Mukherjee, D. Dutta, M. Uzhansky, and E. Koren, "Monolithic In2Se3–In2O3 heterojunction for multibit non-volatile memory and logic operations using optoelectronic inputs," *npj 2D Materials and Applications*, vol. 6, no. 1, p. 37, May 2022.

- [18] T. W. Hickmott, "Low-frequency negative resistance in thin anodic oxide films," *Journal of Applied Physics*, vol. 33, no. 9, pp. 2669–2682, Sep. 1962.

- [19] J. G. Simmons and R. R. Verderber, "New conduction and

reversible memory phenomena in thin insulating films," in *Proc.* the Royal Society of London. Series A. Mathematical and Physical Sciences, vol. 301, no. 1464, pp. 77–102, Oct. 1967.

- [20] S. Q. Liu, N. J. Wu, and A. Ignatiev, "Electric-pulseinduced reversible resistance change effect in magnetoresistive films," *Appl. Phys. Lett.*, vol. 76, no. 19, #2749, May 2000.

- [21] W. W. Zhuang *et al.*, "Novel colossal magnetoresistive thin film nonvolatile resistance random access memory (RRAM)," in *Proc.* of International Electron Devices Meeting, 2002, pp. 193–196.

- [22] A. Žužić, A. Ressler, and J. Macan, "Perovskite oxides as active materials in novel alternatives to well-known technologies: A review," *Ceramics International*, vol. 48, no. 19, pp. 27240– 27261, Oct. 2022.

- [23] L. D. Bozano, B. W. Kean, V. R. Deline, J. R. Salem, and J. C. Scott, "Mechanism for bistability in organic memory elements," *Appl. Phys. Lett.*, vol. 84, no. 4, pp. 607–609, Jan. 2004.

- [24] S. Kundu, M. Clavel *et al.*, "Lead-free epitaxial ferroelectric material integration on semiconducting (100) Nbdoped SrTiO3 for low-power non-volatile memory and efficient ultraviolet ray detection," *Sci. Rep.*, vol. 5, no. 1, #12415, Dec. 2015. doi: 10.1038/srep12415.

- [25] H. Liu, Y. Wang, J. Wu, G. Zhang, and Y. Yan, "Oxygen vacancy assisted multiferroic property of Cu doped ZnO films," *Phys. Chem. Chem. Phys.*, vol. 17, no. 14, pp. 9098–9105, Mar. 2015.

- [26] Z. B. Yan, X. Yan, X. Jia *et al.*, "A low-power Si: HfO<sub>2</sub> ferroelectric tunnel memristor for spiking neural networks," *Nano Energy.*, vol. 107, # 108091, Mar. 2023.

- [27] H. Y. Lee, P. S. Chen *et al.*, "Low power and high speed bipolar switching with a thin reactive Ti buffer layer in robust HfO<sub>2</sub> based RRAM," in *Proc. 2008 IEEE International Electron Devices Meeting*, Dec. 2008. doi: 10.1109/IEDM.2008.4796677.

- [28] G. Sassine, S. La Barbera, N. Najjari, M. Minvielle, C. Dubourdieu, and F. Alibart, "Interfacial versus filamentary resistive switching in TiO<sub>2</sub> and HfO<sub>2</sub> devices," *J. Vac. Sci. Technol. B, Nanotechnol. Microelectron. Mater. Process. Meas. Phenom.*, vol. 34, no. 1, #012202, Jan. 2016.

- [29] J. Xiao, T. S. Herng, J. Ding, and K. Zeng, "Resistive switching behavior in copper doped zinc oxide (ZnO:Cu) thin films studied by using scanning probe microscopy techniques," *J. Alloys Compd.*, vol. 709, pp. 535–541, Jun. 2017.

- [30] S. Kim, H. Moon, D. Gupta, S. Yoo, and Y.-K. Choi, "Resistive switching characteristics of Sol–Gel zinc oxide films for flexible memory applications," *IEEE Trans. Electron Devices*, vol. 56, no. 4, pp. 696–699, Apr. 2009.

- [31] S. Tuo, R. Wang, Z. Wu, and Y. Sun, "A review of resistive switching devices: performance improvement, characterization, and applications," *Small Structures*, vol. 2, no. 4, #2000109, Apr. 2021.

- [32] A. Ghosh, N. Kumari, and A. Bhattacharjee, "Influence of Cu doping on the structural, electrical and optical properties of ZnO," *Pramana - J. Phys.*, vol. 84, no. 4, pp. 621–635, Apr. 2015.

- [33] F. M. Simanjuntak *et al.*, "Impacts of Co doping on ZnO transparent switching memory device characteristics," *Appl. Phys. Lett.*, vol. 108, no. 18, #183506, May 2016.

- [34] H. Li, Q. Chen, X. Chen, Q. Mao, J. Xi, and Z. Ji, "Improvement of resistive switching in ZnO film by Ti doping," *Thin Solid Films*, vol. 537, pp. 279–284, Jun. 2013.

- [35] D. Xu, Y. Xiong, M. Tang, and B. Zeng, "Coexistence of the bipolar and unipolar resistive switching behaviors in vanadium doped ZnO films," *J. Alloys Compd.*, vol. 584, pp. 269–272, Jan. 2014.

- [36] C.-C. Lin, Z. L. Tseng *et al.*, "Unipolar resistive switching behavior of Pt/Li x Zn 1-x O/Pt resistive random access memory devices controlled by various defect types," *Appl. Phys. Lett.*, vol. 101, no. 20, #203501, Nov. 2012.

- [37] H. Yu, M. Kim *et al.*, "Al-doped ZnO as a switching layer for transparent bipolar resistive switching memory," *Electron. Mater. Lett.*, vol. 10, no. 2, pp. 321–324, Mar 2014.

- [38] M. H. Tang, Z. Q. Zeng et al., "Resistive switching behavior of La-doped ZnO films for nonvolatile memory applications," *Solid. State. Electron.*, vol. 63, no. 1, pp. 100–104, Sep. 2011.

- [39] K. Marsh and B. Bugusu "Food packaging—roles, materials, and environmental issues," *Journal. Food. Science*, vol. 72, no. 3, pp. 39–55, Apr. 2007.

- [40] R. Muniramaiah, G. Maharana, J. M. Fernandes *et al.*, "Sputterdeposited highly flexible noble metal multi-layer electrode viable

for energy and luminescent devices," *Surfaces and Interfaces*, vol. 39, #102949, Jul. 2023.

- [41] M. Uddin, M. S. Hasan, and G. S. Rose, "On the theoretical analysis of memristor based true random number generator," in *Proc. the 2019 on Great Lakes Symposium on VLSI*, 2019, pp. 21– 26.

- [42] M. Hu, H. Li, Y. Chen *et al.*, "Memristor crossbar-based neuromorphic computing system: A case study," *IEEE Trans. on Neural Networks and Learning Systems*, vol. 25, no. 10, pp. 1864– 78, Jan 2014.

- [43] P. M. Raj, A. Subramaniam, and S. Kundu, "Memristor BJT pair based low complex circuits for portable electronics," *Analog Integrated Circuits and Signal Processing*, vol. 107, no. 2, pp. 239–47, May 2021.

Copyright © 2024 by the authors. This is an open access article distributed under the Creative Commons Attribution License (<u>CC BY-NC-ND 4.0</u>), which permits use, distribution and reproduction in any medium, provided that the article is properly cited, the use is non-commercial and no modifications or adaptations are made.

Panati S Sreenivas Reddy presently pursuing his Ph.D in the Department of Electronics and Communication Engineering, Dr. M.G.R. Educational and Research Institute, Chennai. He has graduated M.E in Applied Electronics in the year 2000 in Madras University and B.E in Electronics and Communication Engineering in the year 1998 in Madras University. He is working as an Associate Professor, Electronics primaring Nalla Narazimba Paddy educational

and Communication Engineering, Nalla Narasimha Reddy educational societies group of institutions, Telangana. He has 21 years of Academic Experience at under graduate and Post graduate level. His research interests include Nanomaterials, Micro Electronics, and VLSI Design.He is a member of IETE and ISTE respectively.

P Michael Preetam Raj is currently working as Associate Professor in the Department of Computer Science & Engineering (CSE), MLR Institute of Technology, Hyderabad. He obtained his Ph.D. in the year 2020 from Birla Institute of Technology and Science, Pilani– Hyderabad Campus, India. He received his B.Tech degree in Department of ECE from JNTUH in 2008 and M.E Applied Electronics Channel Hig aurent proceeds inderests include

from Anna university, Chennai. His current research interests include simulation and fabrication of futuristic Nano electronic devices, circuits and systems. He is a member of Internet Society.

**Sravan K. Vittapu** received his Ph.D. degree in Department of EEE from Birla Institute of Technology and Sciences-Pilani, Hyderabad Campus in 2022, B.Tech. and M.Tech. degrees in the Department of Electronics and Communications Engineering from the JNTUK, AP, India, in 2009 and 2013, respectively. From 2013-2016, he has worked with the Department of Electronics and Communications Engineering, in VBIT under

JNTUH, Telangana, India, as an Assistant Professor. From 2016-2021, He has worked as Teaching Assistant in BITS-Pilani Hyderabad Campus. Currently, he is working as Associate Professor in the Department of ECE, Nalla Narasimha Reddy Education Society's Group of Institutions (Autonomous), Korremula X Road, Via Narapally, Ghatkesar (M), Chowdariguda, Hyderabad, India-500088. His areas of interest include design of memristive based circuits and systems, algorithms and VLSI architectures of image and video coding, Pattern Recognition algorithms. He is a member of International Association of Engineers (IAENG).

**K. Senthil Kumar** is currently working as Professor in ECE Department, Dr. M.G.R. Educational and Research Institute, Chennai since 2000, and specialized in the field of Nano Technology. He received his B.E in 1996 and M.E in 2001 in Department of ECE, Madras University respectively. He received his PhD degree from Jadavpur University in 2013. He published more than 55 Papers in Conferences & Journals. He has guided around

50 Engineering student projects. Since 2015, he was guiding Research Scholars who have registered in Dr. M.G.R Educational and Research Institute, University, Chennai. He is a member of IETE and ISTE.